# Design of a Microcontroller-Based Ethernet Messaging Device

David Clausen, Stanford University December 13, 2000

**Abstract:** I describe the design of a microcontroller-based hardware device which has a standard RJ45 Ethernet port and an LCD display. The device will receive and decode UDP/IP datagrams, and display the contents of those datagrams as text on the LCD display.

# 1. Introduction

## **1.1 Description**

This report is offered as documentation of my final project in EE281, "Embedded System Design Laboratory", in the Fall quarter of 2000 at Stanford University.

For my final project, I wanted to use an AVR AT90S8515 microcontroller to communicate over a standard Ethernet network. As a demonstration application, I decided to make a device which could receive UDP datagrams on an Ethernet interface, and display the contents on an LCD display. I also wrote a small perl script which prompts the user for text input, and sends that text to the device as a properly-formatted UDP datagram. This script can be run from a Windows or Unix computer.

For my in-class demonstration, I had a trivial network consisting of a laptop Windows 98 computer, the microcontroller device, and a 10-base-T crossover cable connecting the two. However, since the device communicates using standard IP, it should have no problems communicating over the Internet at large.

# **1.2 Photographs**

Figure 1: Device POST shows NIC's MAC address and pre-programmed IP address

| 0           | C:\Perl\bin\Perl.exe                                                                                             |       |

|-------------|------------------------------------------------------------------------------------------------------------------|-------|

| 1<br>2<br>3 | ter a 4-line message (20 chars/line<br>>                                                                         | max): |

|             | ur message will look like this:<br>Hello, World!<br>This message is<br>being sent via UDP<br>over 10bT Ethernet! |       |

|             | nding<br>bytes sent.                                                                                             |       |

|             | ter a 4-line message (20 chars/line<br>}<br>}                                                                    | max): |

Figure 2: Compose a message in Win98, and send it via UDP over the Ethernet...

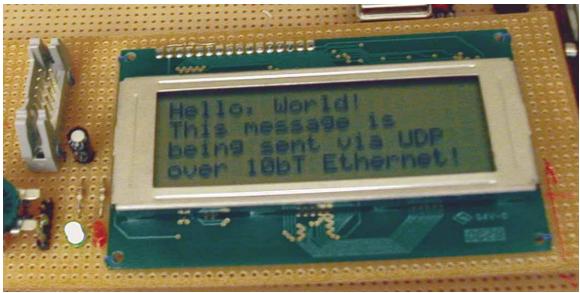

Figure 3: The device receives the UDP message, and displays the contents as ASCII

## 2. High Level Design

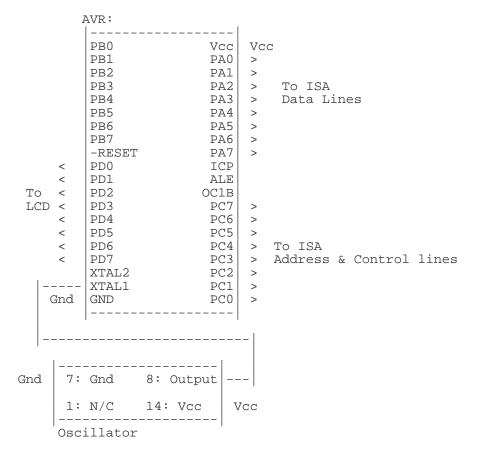

The project uses a generic NE2000-compatible ISA Ethernet card which I bought at a local electronics store. I have connected the card in such a way that it can be controlled by the AVR using 16 logic lines (8 bi-directional data, 5 address, 2 strobes, and 1 reset). After careful reading of numerous spec sheets, and studying the sourcecode for NE2000 drivers on other systems, I was able to write my own set of driver functions for this card in AVR assembly language.

The other main peripheral component in the system is a 4 line x 20 character LCD display. Since these displays are commonly used in microcontroller systems, it was easier to find documentation on how to control them. As with the NE2000, I ended up writing my own driver functions for this device in AVR assembly. This is done using 7 logic lines (4 data, 2 address, 1 strobe).

Sitting in between these two components is the "glue" software which decodes UDP datagrams, decodes ARP requests and sends ARP replies, and manages the state of the system.

## 3. Hardware Design

## 3.1. Ethernet Subsystem

The ISA card connector is connected to PORTA and PORTC of the AVR microcontroller. PORTA is used as an 8-bit bi-directional data bus between the Ethernet card and the AVR (D0 - D7 of the ISA spec). The low 5 lines of PORTC are used as address lines (always controlled by the AVR) (ISA A0 - A5). The next two lines are Read and Write strobes (active low, always controlled by the AVR) (ISA -IOR and -IOW). The last line signals a hardware reset to the ethernet card (active high, always controlled by the AVR) (ISA RESET).

The ISA connector has several pins which I have permanently connected either to ground or Vcc. The obvious ones are the power and ground feeds for the card. Also, -SMEMR and -SMEMW are permanently set high (these are active-low strobes for ISA access modes which I don't use). A5-A7, A10-A19, and AEN are permanently tied to ground. A8 and A9 are permanently set high. This combination effectively causes the low 5 address bits (A0 - A4) coming from the AVR to be added to a permanent offset of 0x300, permitting the AVR to address memory locations 0x300 - 0x320 using only 5 address lines. Conveniently, this is exactly the address range used by the NE2000 Ethernet card.

Many of the unused pins on the ISA connector are left unconnected. Among these are several other power lines (+12v, -5v, -12v), many lines for DMA access, IRQ lines, high-order data lines (for 16-bit data transfers), and a few others. One helpful fact was that the designers of the SMC Ethernet card were kind enough to delete the connection pads for the ISA lines which the card ignored. This was a wonderfully helpful indicator of which parts of the ISA spec I needed to worry about in my design, and which I could ignore. The only lines which are used by the NIC, but are unconnected in my design are several of the IRQ lines. Since the card works fine in polling mode, there seems to be no danger in ignoring IRQs set by the card.

The NE2000 NIC itself is used without modification. In fact, I have tried several cards from different manufacturers, and they all seem to work fine. The SMC EZNET-ISA drew the least amount of power, so that was the one I usually used in the system.

## 3.2. LCD Subsystem

The LCD display subsystem was built on its own semi-autonomous daughterboard. It has a 10-pin header which can be connected directly to one of the PORTx connectors on the STK-200 development board using a ribbon cable. I used it this way when I was writing the software to control the LCD. However, since this project does not use the STK-200, I hardwired the LCD daughterboard to PORTD of the embedded AVR. It also requires power and ground, which are connected to the 7805 power circuit. The board has a variable resistor which is used to adjust the contrast of the display, and also a LED power indicator.

## 3.3 Power Subsystem

The power circuit is based on a 7805 5-volt regulator. There is a 200 microfarad capacitor across the inputs, and smaller noise-absorbing capacitors near each component.

## 3.4 AVR Oscillator

The clock for the AVR is provided by a canned 4MHz oscillator from Pletronics.

# 4. Software Design

## **4.1. Ethernet Driver**

The most challenging part of this project was designing the software to communicate with the Ethernet card. Unfortunately I was only able to find partial specifications for the

card on the internet, and so I had to infer some information about the card's operation by reading sourcecode of drivers for other systems. In addition, I had to learn about and properly control the basic mechanics of the ISA bus - timing issues, access modes, etc.

In summary, the AVR communicates with the card through a set of 32 memory locations. The AVR sets the address lines A0 - A5, then lowers and raises either the read or write strobe, causing a read or write of 8 bits on the data bus. If it was a write, the AVR drives D0 - D7 prior to the write strobe being lowered. If it was a read, the AVR reads values of D0 - D7 just before the read strobe is raised.

The lower half of the addressable memory locations (0x300 - 0x30f) are referred to as "registers" in the Ethernet card's controlling chip. These are documented in the spec sheet for the "National Semiconductor DP8390D Network Interface Controller", which apparently was the chip used in the original NE2000 series of Ethernet cards (this interface has since been reproduced by many card and chipset manufacturers, hence the long line of "NE2000 compatible" or "NE2000 clone" cards like the one I used for this project). Reading from and writing to these registers permits the AVR to configure the card's options, allocate space in the card's onboard RAM, initiate transfers of data between the card and the AVR, etc.

The upper half of the addressable memory locations (0x310 - 0x31f) are used for other purposes. After looking through the sourcecode for a couple of open-source drivers, i was able to infer that 0x310 is the general-purpose data-transfer location.

The card has an internal RAM buffer of 16KB. In order to transfer data to or from the card's onboard RAM, the AVR writes a pointer into one of the card's registers, then writes a memory transfer command to a command register, and then begins repeatedly reading from or writing to location 0x310. After each read or write, the card increments its internal pointer, so subsequent read or write operations to 0x310 actually interact with the next sequential location in the card's internal RAM. Most of this memory is used as a ring buffer to hold received packets, and since both the AVR and the NIC are accessing this memory, you must be careful to keep the set of pointers describing the state of the buffer up to date. Otherwise contention between the two could cause corruption of the data, or the buffer could overflow causing corruption or a card crash.

Another segment of memory is used to build and store packets for transmitting. Again, care is needed to make sure that the AVR and the NIC don't interact badly when accessing this memory.

The only other location which seems to have a significance is 0x31f, which can be written to initiate a software reset (although I do not make use of this in my project -- I use a hardware reset line to force a reset).

There are many other details surrounding the use of the Ethernet card. Refer to my sourcecode and the relevant spec sheets for more information. One important general point is that before using the Ethernet card with a project like this, you have to install it in

a real x86 computer, boot to DOS, and configure the card's EEPROM using the manufacturer's configuration program (which comes on a floppy disk with the card). The card must be put into non-plug-n-play mode, and you need to fix the I/O base address to 0x300 (or whatever value matches your hard-wired address offset).

## 4.2. Ethernet/802.3, UDP/IP stack

In addition to dealing with the NIC, the software must also transmit and receive properlyformatted data packets in order to participate on the network. Since the NE2000 NIC only provides raw bytes from the packets, it is up to my software to decode the Ethernet frame headers, as well as ARP and IP packet formats.

The device has both an Ethernet MAC address, and an IPv4 address. The MAC address is read out of the NIC's EEPROM during initialization of the card. Oddly, the device driver must read the MAC address from the card's EEPROM, and then write it back to several of the card's registers as part of the bootup sequence. The IP address is simply hardcoded into my software. For the testing and demonstration, I used an address in a private block: 192.168.0.14.

The first protocol the device must understand in order to participate on the network is ARP. The ARP protocol is used to discover the MAC address of a device on the network, when only the IP address is known to the sender. Since the AVR has a tiny amount of onboard RAM, the software decodes packets in a pipeline fashion -- reading one byte at a time, and jumping to the appropriate code as soon as a decision can be made about the type of packet, where the code continues to read out bytes from the NIC. The ARP-request handling code immediately sends a properly formatted ARP reply packet.

Additionally, the device receives and decodes UDP messages arriving on port 987. The data portion of these packets are sent byte-by-byte to the LCD device, as described below.

All other incoming packets are simply discarded.

## 4.3. LCD driver

The LCD display has an onboard controller which is compatible with the industrystandard Hitachi interface. From my research, it seems that most LCD displays use this interface. The controller uses either 4 or 8 lines as a bi-directional communication bus. I use the 4-bit mode to reduce the number of pins on the AVR which are dedicated to driving the LCD. There are 3 additional lines: "RS: register select", "RW: read/write", and "E: enable". In short, RS indicates whether the bus is being used to transmit a command or data. RW indicates whether the AVR is reading from or writing to the LCD controller. E is a strobe which is used to indicate when the values on the other pins are known to be stable. All 3 control lines are always set by the AVR. The 4 or 8 bus lines can be set by either the AVR or the LCD, depending on the operation. In "4-bit" mode, data is always sent in two 4-byte nybbles, high byte first. When the system powers up, I follow the initial startup sequence from the part's spec sheet. When a message arrives from the Ethernet, I issue a command to position the LCD's cursor at the top-left position, print 20 characters, reposition the cursor to the beginning of the next line, print 20 characters, and so on. Each message is presumed to be exactly 80 characters in length. Longer messages are truncated. Shorter messages would cause random values to be written to the display.

The spec sheet states that the Hitachi controller is rather slow, and you must be careful not send a new command or data byte until it has finished processing the last message. This can be done either by waiting for a certain number of microseconds between each transfer, or by reading a busy-flag value from the controller to find out when it is ready. I took the easy way out, and simply delay for the prescribed amount of time after each transfer.

#### 5. Results

I am very pleased with the results of my efforts. The device does what it is supposed to do, and I am not aware of any bugs.

That being said, this is clearly a "first cut" of both the hardware and software. It is apparently possible to memory-map the ISA bus into some portion of the AVR's external memory locations. This way, you can use the AVR's built in address logic, strobes, etc. to communicate with the ISA device, which would simplify the software and speed up access to the NIC. Also, this would permit you to share the memory bus with other devices or an external SRAM chip. In the next revision, I would like to modify my hardware to support this mode of operation.

My software is also sub-optimal. I was very generous with my timing delays, and not terribly concerned with memory use or code beautification. My only concern in this revision was getting everything to work before the deadline. Now that I know how to do it, I think it would be best to simply start over and write new software from scratch for the next revision.

It would also be nice to have more network functionality available. A full TCP/IP stack is probably out of the question, but a minimal implementation, along with a basic socket library is probably quite reasonable.

The last thing I would really like to do is to use this Ethernet subsystem as a component in a more interesting device. Displaying text messages on an LCD is a good demonstration, but in practical terms it is a fairly useless device. One can imagine many other far more interesting Internet-Enabled devices which could be built with these components.

## 6. Parts List

- \* AVR 8515 microcontroller (Atmel AT90S8515-8PC-0033)

- \* NE2000-compatible ISA bus Ethernet card (SMC EZNET ISA)

- \* 4 line x 20 column LCD display (AND 721GST)

- \* 4MHz oscillator (Pletronics P1100-HC from Jameco)

- \* 7805 5v linear voltage regulator (Radio Shack 276-1770A)

- \* 220 microfarad electrolytic capacitor (Radio Shack 272-1029)

- \* 0.1 microfarad capacitors (Radio Shack 272-109A)

- \* ISA card edge connector (Jameco 42091)

- \* Perfboard (Radio Shack 276-1396A)

- \* Wire-wrap Sockets

- \* 2.5K-ohm variable resistor for LCD contrast

- \* LED and 1K-ohm resistor to indicate power is active

- \* Power switch

- \* Power connector

- \* 12v DC "brick" power transformer

# 7. Schematic

# 7.1 ISA connector

| /.1 10/1 0                              | onnector                                                                                                                                                                                    |                                                                                                                                            |                                                                                      |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Gnd<br>AVR-PC7<br>Vcc                   | Gnd<br>RESET<br>+5v<br>IRQ9<br>-5v<br>DREQ2<br>-12v<br>-0WS<br>Gnd                                                                                                                          | -IOCHCK<br>D7<br>D6<br>D5<br>D4<br>D3<br>D2<br>D1<br>D0                                                                                    | AVR-PA7<br>AVR-PA6<br>AVR-PA5<br>AVR-PA4<br>AVR-PA3<br>AVR-PA2<br>AVR-PA2<br>AVR-PA1 |

| Vcc<br>Vcc<br>AVR-PC6<br>AVR-PC5<br>Vcc | +12v<br>-SMEMW<br>-SMEMR<br>-IOW<br>-IOR<br>-DACK3<br>DRQ3<br>-DACK1<br>DRQ1<br>-REFSH<br>CLK<br>IRQ7<br>IRQ6<br>IRQ5<br>IRQ4<br>IRQ5<br>IRQ4<br>IRQ3<br>-DACK2<br>TC<br>BALE<br>+5v<br>OSC | IOCHRDY<br>AEN<br>A19<br>A18<br>A17<br>A16<br>A15<br>A14<br>A13<br>A12<br>A11<br>A10<br>A9<br>A8<br>A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1 | Gnd<br>Gnd<br>Gnd<br>Gnd<br>Gnd<br>Gnd<br>Gnd<br>Gnd<br>Gnd<br>Gnd                   |

| Gnd                                     | to thi                                                                                                                                                                                      | A0<br><br>nection<br>s part<br>le ISA<br>ctor                                                                                              | AVR-PC0                                                                              |

| <b>7.2 LCD</b><br>LCD:                                                  | Contrast-control potentiomete:                                                                                                                | r: |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1: Gnd<br>2: Vdd<br>3: Vo<br>4: RS<br>5: RW<br>6: E<br>7: DB0<br>8: DB1 | Gnd       Vcc         Vcc       /         AVR-PD2       /         AVR-PD3       /         Gnd       /         Gnd       /         Gnd       / |    |

| 9: DB2<br>10: DB3<br>11: DB4<br>12: DB5<br>13: DB6<br>14: DB7           | AVR-PD4<br>AVR-PD5<br>AVR-PD6<br>AVR-PD7                                                                                                      |    |

#### 7.2 AVR + Oscillator

#### 8. Code 8.1. udpsend.pl

```

#!/usr/local/bin/perl -w

use strict;

use Socket;

my $paddr;

sub udpinit();

sub gui();

sub udpsend($);

udpinit();

while(1) {

gui();

éxit(0);

sub udpinit() {

my $proto = getprotobyname('udp');

socket(SOCKET, PF_INET, SOCK_DGRAM, $proto);

my $remote = "192.168.0.14";

my $port = 987;

my $iaddr = gethostbyname($remote);

$paddr = sockaddr_in($port, $iaddr);

}

sub gui() {

$| = 1;

print "enter a 4-line message (20 chars/line max):\n";

my $pad = ' ' x 20;

my @lines = ();

my $line;

print " >....<\n";

while (@lines < 4) {</pre>

print scalar(@lines)+1, " >";

$line = <STDIN>;

chomp($line);

$line .= $pad;

$line = substr($line, 0, 20);

push(@lines, $line);

}

print "\n\n Your message will look like this:\n";

print " |-----|\n";

foreach my $line (@lines) {

print " | ", $line, " |\n";

}

print " |-----|\n";

my $message = join('', @lines);

print "\nSending...\n";

my $bytecount = udpsend($message);

print $bytecount, " bytes sent.\n\n";

}

sub udpsend($) {

my $message = $_[0];

my $bytecount = send(SOCKET, $message, 0, $paddr);

return($bytecount);

}

```

#### 8.2. avr-ne2k.asm

```

_____

:----

; dave clausen

; ee281

; avr-ne2k.asm

; 11/26/2000

;______

; setup

;______

.nolist

.include "8515def.inc"

.list

; _____

; register definitions

.def ZERO = r2

.def ONE = r3

.def FF = r4

.def LED = r5

_____

; constants

_____

; *** TCD ***

; refer to AND "intelligent alphanumeric application notes" PDF document

; for a description of the LCD command API. (can be downloaded from

; http://www.purdyelectronics.com/).

; the brief summary: there are two modes for accessing the LCD:

; 4-bit and 8-bit. in addition, you need three extra control lines,

; so really these modes should be called 7-bit and 11-bit.

; anyway, to conserve pins on my AVR, i am using the slightly more

; complex 4-bit interface. the two modes are similar - the main difference

; is that in 4-bit mode, you send data in two chunks - the 4 high bits, ; followed immediately afterwards by the 4 low bits. the initialization

; sequence for 4-bit mode is a little different also.

; regardless of which mode you use, you follow the same rules:

; the RS line tells the LCD which register (instruction or data) you whish

; to access.

; the RW bit tells the LCD whether you are reading or writing.

; the 4 (or 8) DB lines contain the binary data being written to, or read

; from the register.

; the E line goes through a state change, indicating that the data on the

; other lines is valid and holding steady. to make life easy, i always

; set the E line low, then high, then low, while holding all of the other

; lines constant. (see the API doc for a more efficient technique).

; I have wired my controller so that it can be plugged into one of the

; 10-pin headers on the STK-200 development board. Pin 0 is not

; connected to anything (maybe later i will add an LED or a button or

; something). Pin 1 is tied to the "E" line on the LCD. Pin 2 is tied

; to the RS bit. Pin 3 is tied to the RW bit, and pins 4-7 are tied

; to DB4-DB7 on the LCD.

```

| .equ | LED_BIT = | 0b0000001 | ; bit | used | for | the | red | LED |  |

|------|-----------|-----------|-------|------|-----|-----|-----|-----|--|

|------|-----------|-----------|-------|------|-----|-----|-----|-----|--|

; bits used by the LCD interface

; the "E" bit (enable) .equ 0b0000010 ENABLE\_BIT = .equ ; the "RS" bit (register select) RS BIT = 0b00000100 .equ RW\_BIT = ; the "R/W" bit (read or write select) 0b00001000 .equ DB\_BITS = 0b11110000 ; the 4 data bits .equ  $NOT\_LCD\_BITS = 0b0000001$ .equ NOT\_ENABLE\_BIT =0b1111101 NOT\_RS\_BIT = 0b1111101 .equ .equ NOT\_RW\_BIT = .equ 0b11110111 0b00001111 NOT\_DB\_BITS = .equ ; which port is the LCD using? .equ LCD\_PORT = PORTD LCD PORT DDR = DDRD .equ ; \*\*\* NE2000 ethernet card \*\*\* ; internal command registers for the DP8390 chip. ; definitions are taken from National Semiconductor document ; DP8390D.pdf: "DP8390D/NS32490D NIC Network Interface Controlloer" ; (this is the datasheet for the DP8390D chip, which was used in ; the original NE2000 cards). ; hardware has the base address hardwired. the software ; only needs to set the lowest 5 bits NE2K\_BASE = 0 .equ ; internal registers (see page 17 of DP8390D.pdf). ; these are defined here for completeness. i doubt i will need to use ; all of them in the code. ; Page 0 readable registers .equ  $NE2K_CR =$ NE2K\_BASE + 0 ; command register NE2K BASE + 1 ; current local DMA address 0 NE2K CLDA0 = .equ ; local dma 1 NE2K\_CLDA1 = .equ NE2K\_BASE + 2 NE2K\_BNRY = NE2K\_BASE + 3 ; boundary pointer

; transmit status register .equ NE2K\_BASE + 4 NE2K TSR = .equ .equ  $NE2K_NCR =$ NE2K\_BASE + 5 ; number of collisions register ; FIFO NE2K\_BASE + 6 NE2K\_BASE + 7 NE2K\_FIFO = NE2K\_ISR = .equ .equ ; interrupt status register NE2K\_CRDA0 = NE2K\_BASE + 8 ; current remote DMA address 0 .equ NE2K\_CRDA1 = NE2K\_BASE + 9 ; remote DMA 1 ; reserved .equ NE2K\_RESV1 = NE2K\_BASE + 10 .equ NE2K\_BASE + 11 ; reserved NE2K RESV2 = .equ .equ NE2K\_RSR = NE2K\_BASE + 12 ; receive status register NE2K\_CNTR0 = NE2K\_BASE + 13 ; tally counter 0 (frame alignment .equ errors) NE2K CNTR1 = NE2K\_BASE + 14 ; tally counter 1 (CRC errors) .equ NE2K\_CNTR2 = NE2K\_BASE + 15 ; tally counter 2 (missed packet errors) .equ ; Page 0 writable registers ; +0: CR is read/write NE2K PSTART = NE2K BASE + 1 ; page start register . eau NE2K PSTOP = NE2K\_BASE + 2 .equ ; page stop register ; +3: BNRY is read/write NE2K\_TPSR = NE2K\_TBCR0 = NE2K BASE + 4 ; transmit page start address .equ NE2K\_BASE + 5 ; transmit byte count register 0 .equ .equ NE2K\_TBCR1 = NE2K\_BASE + 6 ; transmit byte count register 1 ; +7: ISR is read/write .equ  $NE2K_RSAR0 =$ NE2K\_BASE + 8 ; remote start address register 0 .equ NE2K RSAR1 = NE2K BASE + 9 ; remote start address register 1 NE2K\_RBCR0 = NE2K\_BASE + 10 ; remote byte count register 0 .equ NE2K\_BASE + 11 ; remote byte count register 1 NE2K\_BASE + 12 ; receive configuration register .equ NE2K\_RBCR1 = NE2K RCR = .equ .equ  $NE2K_TCR =$ NE2K\_BASE + 13 ; transmit configuration register  $NE2K_DCR =$ NE2K\_BASE + 14 ; data configuration register NE2K\_BASE + 15 ; interrupt mask register .equ NE2K\_IMR = .equ

LCD BITS =

0b11111110

; Page 1 registers ; +0: CR spans pages 0,1, and 2 NE2K\_BASE + 1 NE2K\_PAR0 = ; physical address register 0 .equ .equ NE2K PAR1 = NE2K BASE + 2 ; physical address register 1 NE2K\_BASE + 3 ; physical address register 2 NE2K\_PAR2 = .equ ; physical address register 3

; physical address register 4 NE2K\_PAR3 = NE2K\_BASE + 4 .equ NE2K\_BASE + 4 NE2K\_BASE + 5 NE2K\_BASE + 6 NE2K PAR4 = .equ NE2K\_PAR5 = ; physical address register 5 .equ NE2K\_BASE + 7 ; current page register NE2K\_BASE + 8 ; multicast address register 0  $NE2K_CURR =$ .equ .equ  $NE2K_MAR0 =$ NE2K\_MAR1 = NE2K\_BASE + 8 ; multicast address register 1 .equ NE2K\_BASE + 10 ; multicast address register 2 NE2K\_BASE + 11 ; multicast address register 3 NE2K\_BASE + 12 ; multicast address register 4 NE2K\_MAR2 = .equ NE2K\_MAR3 = .equ NE2K MAR4 = .equ NE2K\_BASE + 13 ; multicast address register 5 .equ NE2K\_MAR5 = NE2K\_BASE + 14 ; multicast address register 6 NE2K\_BASE + 15 ; multicast address register 7 .equ NE2K MAR6 =  $NE2K_MAR7 =$ .equ ; Page 2 registers ; ... not implemented ... ; Page 3 registers ; ... not implemented ... ; other special locations NE2K\_DATAPORT = NE2K\_BASE + 0x10 .equ NE2K\_BASE + 0x20 NE2K\_BASE + 0x1f .equ NE2K RESET = NE2K\_IO\_EXTENT = ;.equ ; bits in various registers  $NE2K_CR_STOP = 0x01$ ; stop card .equ  $NE2K_CR_START = 0x02$ .equ ; start card ; transmit packet  $NE2K_CR_TRANSMIT = 0x04$ .equ ; remote DMA read  $NE2K_CR_DMAREAD = 0x08$ .equ  $NE2K_CR_DMAWRITE = 0x10$ ; remote DMA write .equ NE2K CR NODMA =  $0 \times 20$ ; abort/complete remote DMA .eau  $NE2K_CR_PAGE0 = 0x00$ .equ ; select register page 0  $NE2K_CR_PAGE1 = 0x40$ ; select register page 1 .equ ; select register page 2  $NE2K_CR_PAGE2 = 0x80$ .equ . eau NE2K RCR BCAST =  $0 \times 04$  $NE2K_RCR_MCAST = 0x08$ .equ  $NE2K_RCR_PROMISCUOUS = 0x10$ .equ  $NE2K_RCR_MONITOR = 0x20$ .equ .equ  $NE2K_DCR_BYTEDMA = 0x00$  $NE2K_DCR_WORDDMA = 0x01$ .equ  $NE2K_DCR_NOLPBK = 0x08$ .equ  $NE2K_DCR_FIFO2 = 0x00$ .equ  $NE2K_DCR_FIFO4 = 0x20$ .equ .equ  $NE2K_DCR_FIF08 = 0x40$  $NE2K_DCR_FIF012 = 0x60$ .equ  $NE2K_TCR_NOLPBK = 0x00$ .equ  $NE2K_TCR_INTLPBK = 0x02$ .equ .equ  $NE2K_TCR_EXTLPBK = 0x04$ .equ NE2K TCR EXTLPBK2 =  $0 \times 06$ ; i don't have a spec sheet on it, but it seems that the ne2000 cards have 16kb

; of onboard ram mapped to locations 0x4000 - 0x8000. this is used as a buffer ; for packets, either before transmission, or after reception. the DP8390D spec ; sheet describes how the chip manages the buffer space. in summary, you need to ; mark off a relatively small section for your transmit buffer. it seems that ; you can use a chunk either at the beginning or the end of the ram segment. 6 ; pages is the typical size. you then use the rest of the remaining space as a ; receive buffer. the chip treats this as a ring - in other words if it reaches ; the end of the space, it wraps around to the beginning and continues filling ; from there. you need to empty the data out fast enough, otherwise it will ; wrap around and hit itself in the tail. (it will detect this sitaution, and

; just drop incoming data until you clear out some space). there are several ; pointers which are used to keep track of all this. read the datashet for more ; details.  $NE2K_TRANSMIT_BUFFER = 0x40$ ; transmit buffer from 0x4000 - 0x45ff. .equ ; we could add a second 6-bage buffer ; here to do ping-pong (back-to-back) ; transmissions, but lets leave that for ; later... NE2K\_START\_PAGE = 0x46 ; receive buffer ring from 0x80 ; 0x4600-0x7fff .equ .equ NE2K\_STOP\_PAGE = ; port assignments NE2K\_DATA\_OUT = PORTA .equ NE2K\_DATA\_IN = PINA .equ NE2K\_DATA\_DDR = DDRA .equ NE2K\_ADDR\_OUT = PORTC .equ  $NE2K\_ADDR\_DDR = DDRC$ .equ  $NE2K_{ISA}ADDR = 0b00011111$ .equ NE2K\_ISA\_IOR = 0b00100000 NE2K\_ISA\_IOW = 0b0100000 .equ .equ NE2K\_ISA\_RESET =0b10000000 .equ ; hardcoded IP address: NE2K\_IP\_OCTET\_1 = NE2K\_IP\_OCTET\_2 = NE2K\_IP\_OCTET\_3 = 192 .equ 168 .equ 0 .equ .equ NE2K\_IP\_OCTET\_4 = 14 ; which UDP port number should i listen on? NE2K\_LISTEN\_PORT = 987 .equ ; begin eeprom segment . ESEG .db "This is some stuff in the eeprom" .db 0 ; begin data segment ; \_ \_ \_ \_ \_ \_ \_ \_ -----.DSEG ; allocate space in the microcontroller's onboard ram for these things nelk\_mac\_addr:.byte 6; my hardware ethernet addressnelk\_ip\_addr:.byte 4; my ip addressnelk\_peer\_mac\_addr:.byte 6; my partner's hardware ethernet addressnelk\_peer\_ip\_addr:.byte 6; my partner's hardware ethernet address ;-----; begin code segment ; -----\_\_\_\_\_ . CSEG ; interrupt vector ; ---------rjmp RESET ; external reset rjmp IGNORE\_INTERRUPT ; external int0 rjmp IGNORE\_INTERRUPT ; external int1

```

IGNORE_INTERRUPT

; timer2 compare match

rjmp

IGNORE_INTERRUPT

rjmp

rjmp

IGNORE_INTERRUPT

rjmp

IGNORE_INTERRUPT

; timer1 compare match B

; timer1 overflow

; timer0 overflow

IGNORE_INTERRUPT

rjmp

IGNORE_INTERRUPT

IGNORE_INTERRUPT

rjmp

rjmp

; SPI serial transfer complete

; UART, Rx complete

; UART data register empty

; UART, Tx complete

; DRT, Tx complete

rjmp

IGNORE_INTERRUPT

rjmp

IGNORE_INTERRUPT

rjmp

IGNORE_INTERRUPT

IGNORE_INTERRUPT

rjmp

IGNORE_INTERRUPT

; ADC conversion complete

; EEPROM ready

; Analog comparator

rjmp

IGNORE_INTERRUPT

rjmp

IGNORE_INTERRUPT

rjmp

;______

; interrupt handlers

IGNORE INTERRUPT:

reti

RESET:

rjmp

main_program

;-----

;------

; main program

_____

;-----

main_program:

; block interrupts

cli

; reset the stack pointer

r16,low(RAMEND)

ldi

out

SPL,r16

ldi

r16, high(RAMEND)

SPH, r16

out

; initialize special registers

clr

ZERO

ldi

r16, 1

ONE, r16

r16, $FF

mov

ldi

FF, r16

mov

r16, LED_BIT

LED, r16

LED, ZERO

ldi

; active low (0=on, 1=off)

mov

;mov

; turn off the analog comparator to save power

r16, 0b10000000 ; ACD - analog compare disable

ldi

ACSR, r16

out

; port B is connected to the LEDs on the STK-200

; development board. (active low)

; all bits output

ldi

DDRB, r16

out

; intialize the LCD

rcall initialize_lcd

; show countdown sequence on the STK-200 LEDs

r16, 0b11100111

ldi

out PORTB, r16

rcall delay_1s

r16, 0b11011011

PORTB, r16

ldi

out

rcall delay_1s

```

```

ldi

r16, 0b10111101

PORTB, r16

out

rcall delay_1s

r16, 0b01111110

PORTB, r16

ldi

out

rcall

delay_1s

r16, 0b1111111

PORTB, r16

ldi

out

; intialize the LCD (again)

rcall

initialize_lcd

rcall

write_silly_string

rcall

delay_1s

rcall ne2k_init

rcall ne2k_establish_ip_address

lcd_write_mac_addr

rcall

rcall lcd_write_ip_addr

main_loop:

rcall ne2k_read_packet

rjmp main_loop

-----

; -----

; functions

_____

; --

; *** NE2000 ***

;------

ne2k_write:

; address in r16 (5 bits)

; data in r17 (one byte)

; data will be written to the ne2000 NIC

r18

push

push

r19

; set both address and data ports for output

r18, Oxff

ldi

NE2K_ADDR_DDR, r18

out

out

NE2K_DATA_DDR, r18

; set data lines

NE2K_DATA_OUT, r17

out

; set address lines, plus read/write strobes

r18, r16

r18, NE2K_ISA_ADDR

mov

andi

r18, NE2K_ISA_IOR

ori

r19, r18

r18, NE2K_ISA_IOW

NE2K_ADDR_OUT, r18

mov

ori

; IOW high

out

nop

nop

nop

nop

NE2K_ADDR_OUT, r19

; IOW low

out

nop

nop

nop

nop

NE2K_ADDR_OUT, r18

; IOW high

out

r19

pop

рор

r18

ret

```

```

ne2k read:

; address in r16 (5 bits)

; data read from the ne2000 NIC will be put into r17 (1 byte)

push

r18

r19

push

; set address port for output

ldi

r18, Oxff

NE2K_ADDR_DDR, r18

out

; set data port for input

ldi

r18, 0

NE2K_DATA_DDR, r18

out

; set address lines, plus read/write strobes

r18, r16

r18, NE2K_ISA_ADDR

mov

andi

r18, NE2K_ISA_IOW

ori

r19, r18

r18, NE2K_ISA_IOR

NE2K_ADDR_OUT, r18

mov

ori

out

; IOR high

nop

nop

nop

nop

NE2K_ADDR_OUT, r19

; IOR low

out

nop

nop

nop

nop

in

r17, NE2K_DATA_IN

NE2K_ADDR_OUT, r18

; IOR high

out

рор

r19

r18

pop

ret

;-----

ne2k hard reset:

; set, then clear, the ISA RESET line, forcing a hard reset of the card

r18

push

; set address port for output

ldi

r18, 0xff

out

NE2K_ADDR_DDR, r18

; reset line high

ldi

r18, NE2K_ISA_RESET | NE2K_ISA_IOR | NE2K_ISA_IOW

NE2K_ADDR_OUT, r18

out

; is this the right delay? i have no idea,

rcall delay_100ms

; but it works ok

; reset line low

r18, NE2K_ISA_IOR | NE2K_ISA_IOW

ldi

NE2K_ADDR_OUT, r18

out

rcall

delay_100ms ; another arbitrary delay

рор

r18

ret

;-----

ne2k_soft_reset:

; untested. i saw this in someone's driver.

push r16

```

r17 push ldi r16, NE2K\_RESET r16, Oxff ldi rcall ne2k\_write delay\_25ms; rcall pop r17 рор r16 ret ne2k\_show\_cr: ; primitive debugging feature ; read the ne2000 command register, and show it on the STK-200 portB LEDs push r16 push r17 ldi r17, 0b10101010 PORTB, r17 out r16, NE2K\_CR ldi ne2k\_read r17, FF rcall eor PORTB, r17 ; display the command register out delay\_1s rcall ; wait r17 pop pop r16 ret ne2k\_init: ; follow the initialization sequence described on page 19 of ; DP8390D.pdf (er, i mean "sort of" follow). lots of modifications, ; taken mostly from the linux driver. comments indicate interesting ; deviations in cheung's driver, the national semiconductor sample ; driver, and the linux driver, r16 push push r17 push r18 push r30 r31 push ; my step Oa: force a hardware reset on the card rcall ne2k\_hard\_reset ; my step 0b: read mac address from the card's onboard eeprom ne2k\_read\_mac\_eeprom rcall ; read the mac address from the eeprom ; step 1: program command register for page 0 ; cheung, ns 0x21 r16, NE2K\_CR ldi r17, NE2K\_CR\_PAGE0 | NE2K\_CR\_STOP | NE2K\_CR\_NODMA ldi rcall ne2k\_write ; cheung does a soft reset here... ; step 2: initialize data configuration register ; cheung 0x48, ns 0x58 r16, NE2K\_DCR r17, NE2K\_DCR\_BYTEDMA | NE2K\_DCR\_FIF08 | NE2K\_DCR\_NOLPBK ldi ldi ne2k\_write rcall ; step 3: clear remote byte count registers ; cheung, ns 0 ldi r16, NE2K\_RBCR0 ldi r17, 0 ne2k\_write rcall ldi r16, NE2K\_RBCR1

```

ldi

r17, 0

rcall

ne2k_write

; step 4: initialize recieve configuration register

; cheung: 0x0c, ns: 0, linux: 0x20

r16, NE2K_RCR

r17, NE2K_RCR_BCAST

ldi

;ldi

ldi

r17, NE2K_RCR_MONITOR

; disable reception for now

ne2k_write

rcall

; step 5: place the NIC in loopback mode (hey - don't i also have to set

; a bit in DCR in order to go into loopback mode? hmm...)

r16, NE2K_TCR

r17, NE2K_TCR_INTLPBK

ldi

ldi

rcall

ne2k_write

; step 5 and a half: initialize the transmit buffer start page

r16, NE2K_TPSR

ldi

ldi

r17, NE2K_TRANSMIT_BUFFER

rcall

ne2k_write

; step 6: initialize receive buffer ring (256 byte blocks)

; cheung: start=0x40, stop=0x76 (or 0x7c?)

; ns: start=0x26, stop=0x40

; linux: 0x26/0x40 or 0x46/0x80 (NE1SM or NESM)

r16, NE2K_PSTART

r17, NE2K_START_PAGE

ldi

ldi

rcall ne2k_write

ldi

r16, NE2K_BNRY

r17, NE2K_START_PAGE

ldi

rcall

ne2k_write

ldi

r16, NE2K_PSTOP

ldi

r17, NE2K_STOP_PAGE

rcall

ne2k_write

; step 7: clear interrupt status register

; cheung: performs this step earlier (after step #3)

r16, NE2K_ISR

r17, 0xff

ldi

ldi

rcall

ne2k_write

; step 8: initialize the interrupt mask register

; cheung: 0 (out of order - after #7)

; ns: 0x0b

ldi

r16, NE2K_IMR

ldi

r17, 0

; no interrupts, please

rcall ne2k_write

; step 9a: go to register page 1

ldi

r16, NE2K_CR

r17, NE2K_CR_PAGE1 | NE2K_CR_STOP | NE2K_CR_NODMA

ldi

rcall

ne2k_write

; step 9b: initialize hardware address

; (what?! shouldn't this already be set from EEPROM?)

ldi r30,low(ne2k_mac_addr)

; Load Z register low

ldi r31,high(ne2k_mac_addr)

; Load Z register high

ldi

r16, NE2K_PAR0

ld

r17, Z+

rcall

ne2k_write

r16, NE2K_PAR1

r17, Z+

ne2k_write

ldi

ld

rcall

r16, NE2K_PAR2

r17, Z+

ldi

ld

rcall

ne2k_write

```

```

ldi

r16, NE2K_PAR3

ld

r17, Z+

ne2k_write

rcall

r16, NE2K_PAR4

r17, Z+

ldi

ld

rcall

ne2k_write

ldi

r16, NE2K_PAR5

r17, Z+

ld

rcall

ne2k_write

; step 9c: initialize multicast address (i don't care about multicast)

; ... not implemented ...

; step 9d: initialize CURRent pointer

ldi

r16, NE2K_CURR

ldi

r17, NE2K_START_PAGE

rcall

ne2k_write

; step 10: put NIC in START mode

r16, NE2K_CR

r17, NE2K_CR_PAGE0 | NE2K_CR_START | NE2K_CR_NODMA

ldi

ldi

rcall

ne2k_write

; step 11: initialize transmit control register (disable loopback mode)

r16, NE2K_TCR

ldi

ldi

r17, NE2K_TCR_NOLPBK

rcall

ne2k_write

; should i re-set DCR here to cancel loopback?

; my step 12: initialize recieve configuration register so that we can

; get packets

r16, NE2K_RCR

r17, NE2K_RCR_BCAST

ne2k_write

ldi

ldi

rcall

; cheung reads the mac address from eeprom here. seems too late to me!

рор

r31

r30

qoq

pop

r18

r17

pop

pop

r16

ret

ne2k_read_mac_eeprom:

; read the mac address from the onboard EEPROM.

; store the 6-byte value into the designated RAM location (ne2k_mac_addr).

; copied functionality from linux ne.c driver initialization code.

; apparently the mac address from the nic's onboard eeprom is mapped to

; locations 0x0000 - 0x001f. i wish i had a spec sheet which told me these

; things. it is a pain in the neck to have to infer these facts by reading

; somebody else's sourcecode.

push

r16

push

r17

push

r30

push

r31

ldi r30,low(ne2k_mac_addr)

; Load Z register low

ldi r31,high(ne2k_mac_addr)

; Load Z register high

; set register page 0

r16, NE2K_CR

r17, NE2K_CR_PAGE0 | NE2K_CR_STOP | NE2K_CR_NODMA

ldi

ldi

rcall

ne2k_write

```

; select byte wide transfers ldi r16, NE2K\_DCR ldi r17, NE2K\_DCR\_BYTEDMA | NE2K\_DCR\_FIF08 | NE2K\_DCR\_NOLPBK rcall ne2k\_write ldi r16, NE2K\_RBCR0 ldi r17, 0 rcall ne2k\_write ldi r16, NE2K\_RBCR1 ldi r17, 0 rcall ne2k\_write ldi r16, NE2K\_IMR r17, 0 ne2k\_write ldi rcall ldi r16, NE2K\_ISR ldi r17, Oxff rcall ne2k\_write r16, NE2K\_RCR

r17, NE2K\_RCR\_MONITOR ; receive off ldi ldi rcall ne2k\_write ldi r16, NE2K\_TCR r17, NE2K\_TCR\_INTLPBK ; transmit off ldi rcall ne2k\_write ldi r16, NE2K\_RBCR0 ldi r17, 32 ; intend to read 32 bytes rcall ne2k\_write ldi r16, NE2K\_RBCR1 r17, 0 ldi rcall ne2k\_write ldi r16, NE2K\_RSAR0 ldi r17, 0 rcall ne2k\_write ; low byte of start address (0x0000) r16, NE2K\_RSAR1 r17, 0 ldi ldi ; high byte of start address rcall ne2k\_write ldi r16, NE2K\_CR ldi r17, NE2K\_CR\_PAGE0 | NE2K\_CR\_START | NE2K\_CR\_DMAREAD rcall ne2k\_write ldi r16, NE2K\_DATAPORT rcall ne2k\_read ; for some reason, 2 reads are required, otherwise you get duplicate values. rcall ne2k\_read ; the comments in the linux driver talk ; about values being "doubled up", but ; i don't know why. whatever - it works Z+, r17 st ; this way and i don't have time to ; investigate :) r16, NE2K\_DATAPORT ldi rcall ne2k\_read rcall ne2k\_read Z+, r17 st ldi r16, NE2K\_DATAPORT ne2k\_read rcall rcall ne2k\_read Z+, r17 st ldi r16, NE2K\_DATAPORT

ne2k\_read rcall rcall ne2k\_read

```

st

Z+, r17

r16, NE2K_DATAPORT

ldi

ne2k_read

rcall

ne2k_read

rcall

Z+, r17

st

ldi

r16, NE2K_DATAPORT

rcall

ne2k_read

rcall

ne2k_read

Z+, r17

st

; end (abort) the DMA transfer

ldi

r16, NE2K_CR

r17, NE2K_CR_PAGE0 | NE2K_CR_START | NE2K_CR_NODMA

ldi

rcall

ne2k_write

r31

pop

r30

pop

рор

r17

r16

pop

ret

ne2k_read_packet:

; workhorse loop for processing network traffic.

r10

push

push

r11

push

r12

push

r13

push

r14

push

r15

push

r16

r17

push

push

r18

r19

push

push

r20

r30

push

push

r31

ne2k_read_packet_start:

; goto register page 1

ldi

r16, NE2K_CR

r17, NE2K_CR_PAGE1 | NE2K_CR_START | NE2K_CR_NODMA

ldi

rcall

ne2k_write

; read the CURRent pointer

r16, NE2K_CURR

ne2k_read

ldi

rcall

mov

r10, r17

; copy CURR into r10

; goto register page 0

ldi

r16, NE2K_CR

r17, NE2K_CR_PAGE0 | NE2K_CR_START | NE2K_CR_NODMA

ldi

rcall

ne2k_write

; read the boundary pointer

r16, NE2K_BNRY

ldi

rcall

ne2k_read

mov

r11, r17

; copy BNRY into r11

; compare CURR and BNRY

ср

r10, r11

ne2k_read_packet_data

; if not equal, then there is data

brne

; waiting

; to be read from the receive

; buffer ring.

; otherwise the receive buffer is empty,

rjmp

ne2k_read_packet_end

; so we have nothing to do here.

```

; there is data in the NIC's rx buffer which we need to read out ne2k\_read\_packet\_data: r16, NE2K\_RBCR0 ldi ldi r17, Oxff ; i don't know how many bytes i intend rcall ne2k\_write ; to read, so just set this to the ; maximum r16, NE2K\_RBCR1

r17, 0xff ldi ldi rcall ne2k\_write ldi r16, NE2K\_RSAR0 r17, 0 ldi ; low byte of start address (0) rcall ne2k\_write ldi r16, NE2K\_RSAR1 r17, r11 ; high byte of start address (BNRY) mov rcall ne2k\_write ldi r16, NE2K\_CR ; begin the dma read r17, NE2K\_CR\_PAGE0 | NE2K\_CR\_START | NE2K\_CR\_DMAREAD ldi rcall ne2k\_write ldi r16, NE2K\_DATAPORT ; all dma reads come out of this location ; the first 6 bytes are not part of the actual received ethernet packet. ; instead they contain some status information about the packet from ; the dp8390 chip. (see page 11 of the dp8390d spec) rcall ne2k\_read r12, r17 mov ; receive status code (same structure as ; RSR - the receive status register) rcall ne2k\_read r13, r17 ; next packet pointer mov rcall ne2k\_read r14, r17 mov ; receive byte count low rcall ne2k\_read r15, r17 ; receive byte count high mov ; i probably should check that the status code is "good", but for now ; just assume that it is ok. ; i probably should check that the length is reasonable, but for now ; let's just assume it is ok. ; now start reading the actual ethernet frame. (refer to Stevens "TCP/IP ; Illustrated Volume 1", page 23, for a nice diagram of the ethernet ; frame) rcall ne2k\_read ; destination mac address rcall ne2k\_read ; i'm not paying attention to this, since ; the card should have already discarded ne2k\_read rcall rcall ne2k\_read ; packets not meant for me or broadcast rcall ne2k\_read rcall ne2k\_read ; the next 6 bytes are the source mac address. save this for my reply ldi r31, high(ne2k\_peer\_mac\_addr); Load Z register high rcall ne2k\_read st Z+, r17 rcall ne2k\_read Z+, r17 ne2k\_read st rcall st Z+, r17 rcall ne2k\_read st Z+, r17 rcall ne2k\_read

Z+, r17 st rcall ne2k\_read Z+, r17 st ; figure out if this is an 802.3 or Ethernet frame ne2k\_read rcall ; if this byte is 0x06 or higher, it ldi r18, 0x06 r17, r18 ; must be a "type" field, since a ср ; "length" field cannot be 0x0600 brsh ne2k\_read\_packet\_eth ; (1536) or higher. ; fallthrough: 802.3 frame (longer header) rcall ne2k\_read ; length low byte (ignore) ; DSAP rcall ne2k\_read r18, Oxaa ldi r17, r18 cpse rjmp ne2k\_read\_packet\_cleanup rcall ne2k\_read ; SSAP r18, 0xaa r17, r18 ne2k\_read\_packet\_cleanup ldi cpse rjmp rcall ne2k\_read ; cntl ldi r18, 0x03 r17, r18 cpse rjmp ne2k\_read\_packet\_cleanup rcall ne2k\_read ; org code 1 r18,0 r17, r18 ne2k\_read\_packet\_cleanup ldi cpse rjmp rcall ne2k\_read ; org code 2 r18, 0 r17, r18 ldi cpse rjmp ne2k\_read\_packet\_cleanup rcall ne2k\_read ; org code 3 r18, 0 r17, r18 ldi cpse rjmp ne2k\_read\_packet\_cleanup rcall ne2k\_read ; type ne2k\_read\_packet\_eth: ; look at the "type" field in the ethernet frame. the types i ; understand are 0x0800 (IP) and 0x0806 (ARP) ldi r18, 0x08 ; type high byte r17, r18 ne2k\_read\_packet\_cleanup cpse rjmp rcall ne2k\_read ; type low byte ldi r18, 0x00 ; 0x0800: IP ср r17, r18 ne2k\_read\_packet\_ip breq ldi r18, 0x06 ; 0x0806: ARP r17, r18 ср breq ne2k\_read\_packet\_arp ; fallthrough: some other type which i don't recognize ne2k\_read\_packet\_cleanup rjmp ne2k\_read\_packet\_ip: rjmp ne2k\_read\_packet\_ip2 ; do a long jump

ne2k\_read\_packet\_arp: ; decode an ARP packet, and respond appropriately. ; see Stevens p.56 ; confirm hardware type 0x0001 rcall ne2k\_read ; hardware type high byte ldi r18, 0x00 r17, r18 cpse ne2k\_read\_packet\_cleanup rjmp rcall ne2k\_read ; hardware type low byte r18, 0x01 r17, r18 ne2k\_read\_packet\_cleanup ldi cpse rjmp ; confirm protocol type 0x0800 rcall ne2k\_read ; protocol type high byte r18, 0x08 r17, r18 ldi cpse ne2k\_read\_packet\_cleanup rjmp rcall ne2k\_read ; protocol type low byte r18, 0x00 r17, r18 ldi cpse ne2k\_read\_packet\_cleanup rjmp ; confirm hardware size 6 rcall ne2k\_read r18, 6 r17, r18 ldi cpse ne2k\_read\_packet\_cleanup rjmp ; confirm protocol size 4 rcall ne2k\_read ldi r18, 4 cpse r17, r18 rjmp ne2k\_read\_packet\_cleanup ; confirm op code 0x0001 (ARP request) rcall ne2k\_read r18, 0x00 ldi cpse r17, r18 rjmp ne2k\_read\_packet\_cleanup rcall ne2k\_read r18, 0x01 r17, r18 ldi cpse ne2k\_read\_packet\_cleanup rjmp ; ignore sender's hardware address (we already recorded it) rcall ne2k\_read rcall ne2k\_read rcall ne2k\_read rcall ne2k\_read ne2k\_read rcall ne2k\_read rcall ne2k\_read ; record sender's IP address ; Load Z register low ldi r30,low(ne2k\_peer\_ip\_addr) ldi r31, high(ne2k\_peer\_ip\_addr) ; Load Z register high rcall ne2k\_read st Z+, r17 rcall ne2k\_read st Z+, r17 rcall ne2k\_read st Z+, r17 rcall ne2k\_read Z+, r17 st ; ignore target hardware address (meaningless for this packet type) rcall ne2k\_read rcall ne2k\_read

rcall ne2k\_read rcall ne2k\_read rcall ne2k\_read rcall ne2k\_read ; compare target IP address to our own. if its a match, then we should ; reply with an ARP reply. if it doesn't match, then this packet was ; meant for someone else, so we can ignore it. ; Load Z register low ldi r30,low(ne2k\_ip\_addr) ldi r31,high(ne2k\_ip\_addr) ; Load Z register iow ; Load Z register iow ld r18, Z+ ; read first octet of my IP address rcall ne2k\_read ; read first octet of target IP address cpse r17, r18 ne2k\_read\_packet\_cleanup rjmp ld r18, Z+ ; read next octet of my IP address rcall ne2k\_read ; read next octet of target IP address cpse r17, r18 rimp ne2k\_read\_packet\_cleanup ; read next octet of my IP address ld r18, Z+ rcall ne2k\_read ; read next octet of target IP address cpse r17, r18 rjmp ne2k\_read\_packet\_cleanup r18, Z+ ; read next octet of my IP address ld rcall ne2k\_read ; read next octet of target IP address r17, r18 cpse ne2k\_read\_packet\_cleanup rjmp ; fallthrough: the target IP address is the same as my IP address. ; qoodie! ; i've read all there is to read from this packet. ; end (abort) the DMA transfer ldi r16, NE2K\_CR r17, NE2K\_CR\_PAGE0 | NE2K\_CR\_START | NE2K\_CR\_NODMA ldi rcall ne2k\_write ; update the BNRY (recive buffer ring boundary) pointer. r16, NE2K\_BNRY r17, r13; next packet pointer ldi mov rcall ne2k\_write ; now send an ARP reply packet. ; rcall send\_arp\_reply ; \*\*\*\* ; ... i should test to make sure the card is not transmitting. otherwise i might stomp over the data to be transmitted ... ; ; \*\*\*\* ; set the remote byte count to 60 (arp packets are 60 bytes) ldi r16, NE2K\_RBCR0 ldi r17, 60 rcall ne2k\_write r16, NE2K\_RBCR1 r17, 0 ldi ldi rcall ne2k\_write ldi r16, NE2K\_RSAR0 r17, 0 ldi ; low byte of start address rcall ne2k\_write r16, NE2K\_RSAR1 ldi ldi r17, NE2K\_TRANSMIT\_BUFFER ; high byte of start address rcall ne2k\_write ; begin DMA write

r16, NE2K\_CR ldi ldi r17, NE2K\_CR\_PAGE0 | NE2K\_CR\_START | NE2K\_CR\_DMAWRITE rcall ne2k\_write ldi r16, NE2K\_DATAPORT ; destination hardware address ; Load Z register low ldi r30,low(ne2k\_peer\_mac\_addr) ldi r31,high(ne2k\_peer\_mac\_addr); Load Z register high ld r17, Z+ rcall ne2k\_write ld r17, Z+ rcall ne2k\_write r17, Z+ ld rcall ne2k\_write ld r17, Z+ rcall ne2k\_write r17, Z+ ld rcall ne2k\_write ld r17, Z+ rcall ne2k\_write ; source hardware address ldi r30,low(ne2k\_mac\_addr) ; Load Z register low ldi r31,high(ne2k\_mac\_addr) ; Load Z register high ld r17, Z+ rcall ne2k\_write r17, Z+ ld rcall ne2k\_write ld r17, Z+ rcall ne2k\_write ld r17, Z+ ne2k\_write r17, Z+ rcall ld rcall ne2k\_write r17, Z+ ld rcall ne2k\_write ldi r17, 0x06 rcall ne2k\_write ; hardware type 0x0001 ldi r17, 0x00 rcall ne2k\_write ldi r17, 0x01 rcall ne2k\_write ; protocol type 0x0800 ldi r17, 0x08 rcall ne2k\_write r17, 0x00 ldi rcall ne2k\_write ; hardware size 6 ldi r17,6 rcall ne2k\_write ; protocol size 4 ldi r17,4 rcall ne2k\_write ; op 0x0002 (ARP reply) r17, 0x00 l ne2k\_write ldi rcall ldi r17, 0x02 rcall ne2k\_write ; source hardware address

```

; Load Z register low

ldi r30,low(ne2k_mac_addr)

ldi r31,high(ne2k_mac_addr)

; Load Z register high

ld

r17, Z+

rcall ne2k_write

r17, Z+

ld

rcall

ne2k_write

ld

r17, Z+

rcall ne2k_write

ld

r17, Z+

rcall

ne2k_write

r17, Z+

ld

rcall

ne2k_write

ld r17, Z+

rcall ne2k_write

; source ip address

ldi r30,low(ne2k_ip_addr)

ldi r31, high(ne2k_ip_addr)

; Load Z register low

; Load Z register high

r17, Z+

ne2k_write

ld

rcall

r17, Z+

ld

rcall ne2k_write

ld

r17, Z+

rcall ne2k_write

ld

r17, Z+

rcall ne2k_write

; target hardware address

ldi r31,high(ne2k_peer_mac_addr); Load Z register high

r17, Z+

ld

rcall ne2k_write

ld r17, Z+

rcall ne2k_write

ld

r17, Z+

rcall ne2k_write

ld

r17, Z+

rcall ne2k_write

r17, Z+

ld

rcall

ne2k_write

r17, Z+

ld

rcall ne2k_write

; target ip address

ldi r30,low(ne2k_peer_ip_addr)

; Load Z register low

; Load Z register high

ldi r31,high(ne2k_peer_ip_addr)

ld

r17, Z+

rcall ne2k_write

ld

r17, Z+

rcall ne2k_write

r17, Z+

ld

rcall ne2k_write

ld r17, Z+

rcall ne2k_write

; 18 bytes of padding

ldi r17, 0

rcall ne2k_write

rcall ne2k_write

ne2k_write

rcall

rcall

ne2k_write

rcall

ne2k_write

rcall

ne2k_write

rcall

ne2k_write

rcall

ne2k write

ne2k_write

rcall

rcall

ne2k_write

ne2k_write

rcall

rcall ne2k_write

rcall

ne2k_write

rcall

ne2k_write

rcall ne2k_write

```

```

rcall ne2k_write

rcall ne2k_write

rcall

ne2k_write

; ****

; ... do i need wait for dma to end??? ...

; (see PCtoNIC from natsemi demo driver)

; ****

; end the DMA transfer

ldi

r16, NE2K_CR

r17, NE2K_CR_PAGE0 | NE2K_CR_START | NE2K_CR_NODMA

ldi

rcall

ne2k_write

; how many bytes to send

ldi r16, NE2K_TBCR0

ldi r17, 60

rcall ne2k_write

ldi

r16, NE2K_TBCR1

r17, 0

ldi

rcall ne2k_write

; starting where

ldi

r16, NE2K_TPSR

ldi

r17, NE2K_TRANSMIT_BUFFER

rcall ne2k_write

; issue transmit command!

r16, NE2K_CR

ldi

r17, NE2K_CR_PAGE0 | NE2K_CR_START | NE2K_CR_NODMA |

ldi

NE2K_CR_TRANSMIT

rcall

ne2k_write

rjmp

ne2k_read_packet_cleanup

ne2k_read_packet_ip2:

; decode an IP packet, and respond appropriately

; first process the IP header (Stevens p.34)

; read version and length

rcall ne2k_read

; version (4 bits) + header length (4 bits)

r20, r17; store the header length in r20

mov

r20, 0x0f

; mask out the version part

andi

andi

r17, 0xf0

; mask out the length part

ldi

r18, 0x40

; IPv4 is the only version we accept

r17, r18

ne2k_read_packet_cleanup

cpse

rjmp

rcall ne2k_read

; ignore TOS

rcall ne2k_read

; ignore total length

rcall

ne2k_read

rcall ne2k_read

; ignore identification number

rcall ne2k_read

; ignore fragmentation stuff

rcall

ne2k_read

rcall ne2k_read

rcall

ne2k_read

; ignore TTL

rcall ne2k_read

; read protocol

mov

r19, r17

; save for later in r19

rcall ne2k_read

; ignore checksum

rcall

ne2k_read

; record sender's IP address

```

ldi r31,high(ne2k\_peer\_ip\_addr) ; Load Z register low rcall ne2k read ; Load Z register biol ; Load Z register high rcall ne2k\_read Z+, r17 st rcall ne2k\_read Z+, r17 ne2k\_read st rcall Z+, r17 st rcall ne2k\_read st Z+, r17 ; compare destination IP address to our own. if its a match, then this packet ; is for us. otherwise, this belongs to someone else. ldi r30,low(ne2k ip addr) ; Load Z register low ldi r31, high(ne2k\_ip\_addr) ; Load Z register high r18, Z+ ld ; read first octet of my IP address rcall ne2k\_read ; read first octet of target IP address cpse r17, r18 ne2k\_read\_packet\_cleanup rjmp r18, Z+ ; read next octet of my IP address ld rcall ne2k\_read ; read next octet of target IP address r17, r18 ne2k\_read\_packet\_cleanup cpse rjmp r18, Z+ ; read next octet of my IP address ЪГ rcall ne2k\_read ; read next octet of target IP address r17, r18 cpse rjmp ne2k\_read\_packet\_cleanup ld r18, Z+ ; read next octet of my IP address rcall ne2k\_read ; read next octet of target IP address r17, r18 cpse rjmp ne2k\_read\_packet\_cleanup ; fallthrough: the destination IP address is the same as my IP address. goodie! ; skip over any "options" in the ip header subi r20, 5 ; 5 = size of ip header without any options ; (in 32-bit words) ldi r17, 0 ne2k\_read\_packet\_header1: r20, r17 ср breq ne2k\_read\_packet\_header2 subi r20, 1 ne2k\_read ; read 4-byte option field rcall ne2k\_read rcall rcall ne2k\_read rcall ne2k\_read ne2k\_read\_packet\_header1 rjmp ne2k\_read\_packet\_header2: ; we have now advanced the read pointer up to the first byte of ; the "data" portion of the IP packet ; ok, now look back at the protocol field and jump to the right ; code to handle the packet type r18, 1 ldi ; icmp ср r19, r18 ne2k\_read\_packet\_icmp breq ldi r18, 6 ; tcp r19, r18 ср breq ne2k\_read\_packet\_tcp ldi r18, 17 ; udp r19, r18 ср ne2k\_read\_packet\_udp breq

; fallthrough: unrecognized protocol field (don't expect to get here) ne2k\_read\_packet\_cleanup rjmp ne2k\_read\_packet\_icmp: ; ... icmp not implemented ... r16, 0 r17, 0 ldi ldi rcall move\_cursor ldi r16, 'i' rcall print\_to\_lcd r16, 'c' ldi rcall print\_to\_lcd ldi r16, 'm' rcall print\_to\_lcd ldi r16, 'p' rcall print\_to\_lcd ldi r16, '!' r16, rcall print\_to\_lcd r16, NE2K\_DATAPORT ldi rjmp ne2k\_read\_packet\_cleanup ne2k\_read\_packet\_tcp: ; ... tcp not implemented ... ldi r16, 0 r16, 0 ldi r17, 0 rcall move\_cursor r16, 't' ldi rcall print\_to\_lcd ldi r16, 'c' rcall print\_to\_lcd ldi r16, 'p' print\_to\_lcd r16, '!' rcall ldi r16, rcall print\_to\_lcd r16, NE2K\_DATAPORT ldi ne2k\_read\_packet\_cleanup rjmp ne2k\_read\_packet\_udp: rcall ne2k\_read ; ignore source portnumber rcall ne2k\_read rcall ne2k\_read ; test destination port number r18, high(NE2K\_LISTEN\_PORT) r17, r18 ldi cpse ne2k\_read\_packet\_cleanup rjmp rcall ne2k\_read r18, low(NE2K\_LISTEN\_PORT) ldi r17, r18 cpse ne2k\_read\_packet\_cleanup rjmp rcall ne2k\_read ; ignore udp length rcall ne2k\_read rcall ne2k\_read ; ignore udp checksum rcall ne2k\_read ; now we're finally at the interesting part - the text string to print ; onto the LCD screen. r18, 255 ldi ; start at row #-1 ne2k\_read\_packet\_printloop1: r18 inc ; go to next row cpi r18, 4 ; if we've moved below the end of the ; screen... breq ne2k\_read\_packet\_printloop3 ; ... exit the loop r19, 0 ldi ; go back to column #0 mov r16, r18

r17, r19 mov rcall move\_cursor ; issue carriage return instruction ne2k\_read\_packet\_printloop2: ; increment column pointer inc r19 r19, 21 ; if we've moved off the right of the cpi screen... breq ne2k\_read\_packet\_printloop1 ; ...do a carriage return ldi r16, NE2K\_DATAPORT ; read a byte from the packet rcall ne2k\_read r16, r17 mov rcall print\_to\_lcd ; print it on the screen ne2k\_read\_packet\_printloop2 rjmp ; loop ne2k\_read\_packet\_printloop3: ; voila - the data is on the lcd screen. ignore whatever may be left. rimp ne2k\_read\_packet\_cleanup ne2k\_read\_packet\_cleanup: ; end (abort) the DMA transfer r16, NE2K\_CR ldi r17, NE2K\_CR\_PAGE0 | NE2K\_CR\_START | NE2K\_CR\_NODMA ldi rcall ne2k\_write ; update the BNRY (recive buffer ring boundary) pointer. ; r13 = next packet pointer from NIC packet header. ; note: there seem to be 2 ways of setting this pointer. you can ; set it to one less than the next packet pointer, or equal ; to the next packet pointer. it seems simpler to make it equal -; i'm not sure why you would want to do it the other way. ldi r16, NE2K\_BNRY r17, r13; next packet pointer mov rcall ne2k\_write rcall set\_led\_on rcall delay\_100ms rcall set\_led\_off ne2k\_read\_packet\_end: r31 pop рор r30 r20 pop r19 pop pop r18 r17 pop pop r16 pop r15 рор r14 r13 pop pop r12 r11 pop r10 pop ret ;----ne2k\_establish\_ip\_address: ; stick our hardcoded IP address into the proper spot in the microcontroller's ; RAM ; TBD: replace this routine with a DHCP or BOOTP client! push r16 push r30 r31 push ldi r30,low(ne2k\_ip\_addr) ; Load Z register low

```

ldi r31,high(ne2k_ip_addr) ; Load Z register high

ldi

r16, NE2K_IP_OCTET_1

Z+, r16

st

r16, NE2K_IP_OCTET_2

ldi

Z+, r16

st

r16, NE2K_IP_OCTET_3

ldi

st

Z+, r16

ldi

r16, NE2K_IP_OCTET_4

st

Z+, r16

r31

pop

r30

рор

r16

pop

ret

;-----

; *** LCD ***

; -----

_____

blink_led:

push

r16

ldi

r16, 0

blink_led_loop:

delay_5ms

r16, ONE

rcall

add

cpi

r16, 0

brne

blink_led_loop

ср

LED, ZERO

blink_led_on

breq

rcall set_led_off

r16, 0

ldi

rjmp

blink_led_loop

blink_led_on:

rcall set_led_on

ldi

r16, 0

blink_led_loop

rjmp

pop

r16

ret

set_led_on:

push r16

ldi

rl6, LED_BIT

LED, r16

mov

r16, $FF

ldi

; all I/O pins output

LCD_PORT_DDR, r16

out

r16, LED

mov

out

LCD_PORT, r16

рор

r16

ret

;-----

set_led_off:

push r16

ldi

r16, 0

```

LED, r16 mov r16, \$FF ; all I/O pins output ldi LCD\_PORT\_DDR, r16 out r16, LED mov LCD\_PORT, r16 out r16 pop ret write\_lcd\_ir: ; writes an 8-bit value to the LCD instruction register. ; the value to be written is presumed to be in R16. ; (RS low, R/W low, E high-to-low) r17 push push r18 r19 push push r20 r17, \$FF ; all I/O pins output ldi LCD\_PORT\_DDR, r17 out r17, r16 mov r17, DB\_BITS ; grab the high bits andi r17, LED r18, r17 r18, ENABLE\_BIT or mov ori r19, r16 mov ; grab the low bits... lsl r19 lsl r19 ; ... and shift them up r19 lsl lsl r19 r19, LED or r20, r19 r20, ENABLE\_BIT mov ori ; upper 4 bits (E low) LCD\_PORT, r17 out LCD\_PORT, r18 LCD\_PORT, r17 ; upper 4 bits (E high) ; upper 4 bits (E low) out out ; lower 4 bits (E low) LCD\_PORT, r19 out LCD\_PORT, r20 LCD\_PORT, r19 out ; lower 4 bits (E high) ; lower 4 bits (E low) out r20 pop r19 pop r18 pop r17 pop ret ;\_\_\_\_\_\_ write\_lcd\_dr: ; writes an 8-bit value to the LCD data register. ; the value to be written is presumed to be in R16. ; (RS high, R/W low, E high-to-low) push r17 push r18 push r19 r20 push r17, \$FF ; all I/O pins output ldi out LCD\_PORT\_DDR, r17 r17, r16 mov andi r17, DB\_BITS ; grab the high bits

| ori<br>or<br>mov<br>ori                                                                                             | r17, RS_BIT<br>r17, LED<br>r18, r17<br>r18, ENABLE_BIT                                                                                                                       |                                                                                  |

|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| mov<br>lsl<br>lsl<br>lsl<br>ori<br>or<br>mov<br>ori                                                                 | r19, r16<br>r19<br>r19<br>r19<br>r19, RS_BIT<br>r19, RS_BIT<br>r19, LED<br>r20, r19<br>r20, ENABLE_BIT                                                                       | ; grab the low bits<br>;and shift them up                                        |

| out<br>out<br>out                                                                                                   | LCD_PORT, r17<br>LCD_PORT, r18<br>LCD_PORT, r17                                                                                                                              | ; upper 4 bits (E low)<br>; upper 4 bits (E high)<br>; upper 4 bits (E low)      |

| out<br>out<br>out                                                                                                   | LCD_PORT, r19<br>LCD_PORT, r20<br>LCD_PORT, r19                                                                                                                              | <pre>; lower 4 bits (E low) ; lower 4 bits (E high) ; lower 4 bits (E low)</pre> |

| pop<br>pop<br>pop<br>ret                                                                                            | r20<br>r19<br>r18<br>r17                                                                                                                                                     |                                                                                  |

| read_lcd_ir:<br>ret                                                                                                 |                                                                                                                                                                              |                                                                                  |

| read_lcd_dr:<br>ret                                                                                                 |                                                                                                                                                                              |                                                                                  |

| ;                                                                                                                   |                                                                                                                                                                              |                                                                                  |

| write_silly_str<br>push<br>push                                                                                     | ring:<br>r16<br>r17                                                                                                                                                          |                                                                                  |

| ldi<br>ldi<br>rcall                                                                                                 | r16, 0<br>r17, 0<br>move_cursor                                                                                                                                              | ; row<br>; col                                                                   |

| ldi<br>rcall<br>ldi<br>rcall<br>ldi<br>rcall<br>ldi<br>rcall<br>ldi<br>rcall<br>ldi<br>rcall<br>ldi<br>rcall<br>ldi | <pre>rl6, 'D' print_to_lcd rl6, 'a' print_to_lcd rl6, 'v' print_to_lcd rl6, 'e' print_to_lcd rl6, '' print_to_lcd rl6, 'C' print_to_lcd rl6, 'l' print_to_lcd rl6, 'a'</pre> |                                                                                  |

| rcall<br>ldi<br>rcall<br>ldi<br>rcall<br>ldi<br>rcall<br>ldi<br>rcall                                               | <pre>print_to_lcd rl6, 'u' print_to_lcd rl6, 's' print_to_lcd rl6, 'e' print_to_lcd rl6, 'n' print_to_lcd</pre>                                                              |                                                                                  |

```

rcall

move_cursor

r16, 'E'

ldi

rcall print_to_lcd

r16, 'E'

ldi

print_to_lcd

r16, '2'

rcall

ldi

print_to_lcd

rcall

r16, '8'

print_to_lcd

ldi

rcall

r16, '1'

ldi

rcall

print_to_lcd

ldi

r16, ':'

print_to_lcd

rcall

ldi

r16, 'A'

print_to_lcd

r16, 'V'

print_to_lcd

rcall

ldi

rcall

r16, 'R'

ldi

rcall

print_to_lcd

r16, '-'

ldi

rcall

print_to_lcd

rl6, 'N'

print_to_lcd

ldi

rcall

ldi

r16, 'E'

print_to_lcd

r16, '2'

rcall

ldi

print_to_lcd

rcall

ldi

r16, 'K'

rcall

print_to_lcd

рор

r17

r16

pop

ret

lcd_write_mac_addr:

push

r16

push

r17

r30

push

push

r31

ldi

r16, 2

; row

ldi

r17, 0

; col

rcall move_cursor

ldi

r30,low(ne2k_mac_addr) ; Load Z register low

r31, high(ne2k_mac_addr) ; Load Z register high

ldi

ld

r16, Z+

lcd_print_hex_byte

r16, ':'

print_to_lcd

rcall

ldi

rcall

ld

r16, Z+

lcd_print_hex_byte

rcall

r16, ':'

print_to_lcd

ldi

rcall

ld

r16, Z+

rcall

lcd_print_hex_byte

r16, ':'

ldi

print_to_lcd

rcall

r16, Z+

ld

rcall

lcd_print_hex_byte

r16, ':'

ldi

print_to_lcd

rcall

ld

r16, Z+

lcd_print_hex_byte

rcall

ldi

r16, ':'

rcall

print_to_lcd

ld

r16, Z+

rcall

lcd_print_hex_byte

```

|         | pop<br>pop<br>pop<br>ret                                                                                | r31<br>r30<br>r17<br>r16                                                                                                                                                                                                                     |            |                  |                      |             |

|---------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------|----------------------|-------------|

| ;       |                                                                                                         |                                                                                                                                                                                                                                              |            |                  |                      |             |

| lcd_wri | te_ip_ad<br>push<br>push<br>push<br>push                                                                | r16<br>r17                                                                                                                                                                                                                                   |            |                  |                      |             |

|         | ldi<br>ldi<br>rcall                                                                                     | r16, 3<br>r17, 0<br>move_cursor                                                                                                                                                                                                              | ; r<br>; c |                  |                      |             |

|         | ldi<br>ldi                                                                                              | r30,low(ne2k_ip_addr)<br>r31,high(ne2k_ip_addr)                                                                                                                                                                                              | ; L<br>; L | load Z<br>load Z | register<br>register | low<br>high |

|         | ld<br>rcall<br>ldi<br>rcall<br>ld<br>rcall<br>ld<br>rcall<br>ldi<br>rcall<br>ld<br>rcall<br>ld<br>rcall | <pre>r16, Z+<br/>lcd_print_dec_byte<br/>r16, '.'<br/>print_to_lcd<br/>r16, Z+<br/>lcd_print_dec_byte<br/>r16, '.'<br/>print_to_lcd<br/>r16, Z+<br/>lcd_print_dec_byte<br/>r16, '.'<br/>print_to_lcd<br/>r16, Z+<br/>lcd_print_dec_byte</pre> |            |                  |                      |             |

|         |                                                                                                         | r31<br>r30<br>r17<br>r16                                                                                                                                                                                                                     |            |                  |                      |             |

| ;       |                                                                                                         |                                                                                                                                                                                                                                              |            |                  |                      |             |

|         | nt_hex_b<br>ontains                                                                                     |                                                                                                                                                                                                                                              |            |                  |                      |             |

|         | push<br>push<br>push                                                                                    | r16<br>r17<br>r18                                                                                                                                                                                                                            |            |                  |                      |             |

|         | mov<br>lsr<br>lsr<br>lsr<br>lsr<br>andi                                                                 | r17, r16; MSB<br>r17<br>r17<br>r17<br>r17<br>r17<br>r17, Ob00001111                                                                                                                                                                          |            |                  |                      |             |

|         | mov<br>andi                                                                                             | r18, r16; LSB<br>r18, 0b00001111                                                                                                                                                                                                             |            |                  |                      |             |

|         | mov<br>rcall<br>mov<br>rcall                                                                            | r16, r17<br>lcd_print_hex_nibble<br>r16, r18<br>lcd_print_hex_nibble                                                                                                                                                                         |            |                  |                      |             |

|         | pop<br>pop<br>pop<br>ret                                                                                | r18<br>r17<br>r16                                                                                                                                                                                                                            |            |                  |                      |             |

```

;-----

lcd_print_hex_nibble:

; r16 contains a nibble

push

r16

push

r17

r17, '0'; ascii '0' character

r16, r17

ldi

add

r16, ':'

cpi

brlo

lcd_print_hex_nibble_ok ; if number < 10, can use</pre>

; ascii '0' through '9'

ldi

r17, 'A' - ':'

; jump over some punctuation to get to

; the letters (ABCDEF ascii codes)

add

r16, r17

lcd_print_hex_nibble_ok:

rcall

print_to_lcd

r17

pop

рор

r16

ret

;-----

-----

lcd_print_dec_byte:

; r16 contains a byte

; EEK this is awful code!

r16

push

push

r17

r18

push

r17, r16

mov

dec_byte_200:

ldi

r18, 200

ср

r17, r18

dec_byte_100

r17, r18

r16, '2'

brlo

sub

ldi

print_to_lcd

rcall

rjmp

dec_byte_90

dec_byte_100:

r18, 100

r17, r18